メカトロニクス教材の開発〈その4〉――マイコン実験装置の仕様および実習例について●教材情報

- 烏取県立倉吉高等技術専門校 コンピュータ制御科 川口哲・加藤 明

4.2 ディジタルーアナログ変換回路

時間,温度,湿度などわれわれが日常接している自然界の情報は,そのほとんどが連続した信号であり,アナログ量と呼ばれる。これに対して,コンピュータの内部で処理することのできる情報は不連続で離散的な信号であり,ディジタル量と呼ばれる。コンピュータにより機器制御を行うとき,本来ならばディジタル信号が使用されるべきであるが,その目的あるいは制御対象となる装置の性質上,アナログ信号を必要とする場合も少なくない。このとき,コンピュータにより処理されたディジタル信号を出力機器に適したアナログ信号に変換して供給する技術が求められる。これがディジタルーアナログ変換(以下,「D/A変換」という。)であり,制御技術の重要なポイントの1つとなっている。この節では,マイコン実験装置に組み込まれているD/A変換回路について説明する。

(1) AD7237Aについて

本装置には,D/A変換素子としてアナログデバイセズ社のAD7237Aが組み込まれている。この素子は単独で機能する12ビット電圧出力D/Aコンバー夕(2CH)であり,以下の特徴を有している。

●2CH12ビットD/Aコンバータ

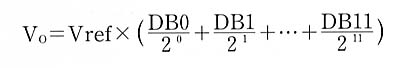

AD7237Aは,現在D/Aコンバータの主流となっているモノリシックCMOS-ICである。分解能は12ビットで,2CHを有するラダー抵抗方式のD/Aコンバータである。図16にD/A変換部の回路図(概略図)を示す。この図でRは抵抗,DB0からDB11はコンピュータより送られる12ビットのディジタル信号を示す。また,ディジタル信号が1のときはスイッチ(SWn)はVref端子側に接続され,0のときはスイッチはGND端子側に接続されることを意味する。このD/Aコンバータはディジタル入力信号の状態によりスイッチのON,OFFを行い,リファレンス電圧を相当の状態に変換して,アナログ信号を出力する。このとき,変換式は次式のようになる。

●電圧リファレンス

AD7237Aは5V±30mVのツェナ電圧リファレンスを内蔵しており,D/Aコンバータのリファレンス電圧として使用することができる。また,この電圧は他部品を駆動するためのリファレンスとしても使用可能であり,最大500μAまでの電流を供給できる。なお,リファレンス電圧は外部からの供給も可能であり,他の高精度リファレンス専用ICなどからの供給を可能にしている。

●出力アンプ

図16に示すように,AD7237Aのアナログ出力部は非反転のCMOSアンプによりバッファされている。このデバイスは0~+5Vまたは0~+10Vのユニポーラ出力範囲と,-5V~+5Vのバイポーラ出力範囲を供給することができる。0~+5V出力設定では,図中のRofs端子をVo端子に接続することにより,入力電圧と等しいアナログ出力を得ることができる。これは,アンプの電圧増幅度が無限大であること,およびアンプヘの入力電流が限りなく0に近いことなどのオペアンプの特性から導き出される。また,0~+10V出力設定では,Rofs端子をGND端子に接続することにより,このアンプは非反転の増幅回路として機能する。その結果,D/Aコンバータを通過した0~+5Vの入力に対して,2倍の出力電圧を生成する。さらに,-5V~+5V出力設定では,Rofs端子をVref端子に接続する。このときアンプヘの入力はユニポーラD/Aコンバータからの正電圧であり,これを非反転増幅して,ハーフスケール分だけオフセットして出力する。この場合,アンプヘはデュアル電源による±12V~±15Vの供給が必要である。

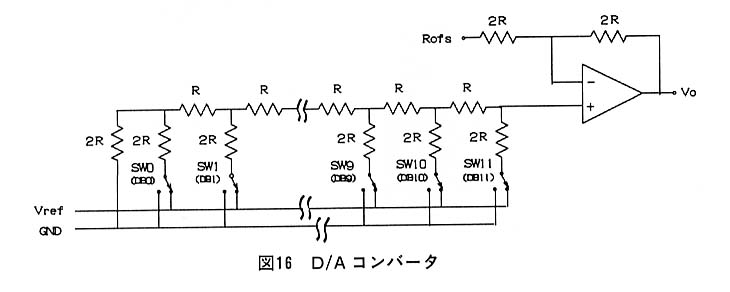

以上の代表例として,表5に0~+10Vのユニポーラ設定時および-5V~+5Vのバイポーラ設定時のコード表を示す。これは,コンピュータ内部で処理された12ビットのディジタル入力信号と,D/A変換後のアナログ出力との関係を示すものである。

●12ビットデータのロード構造

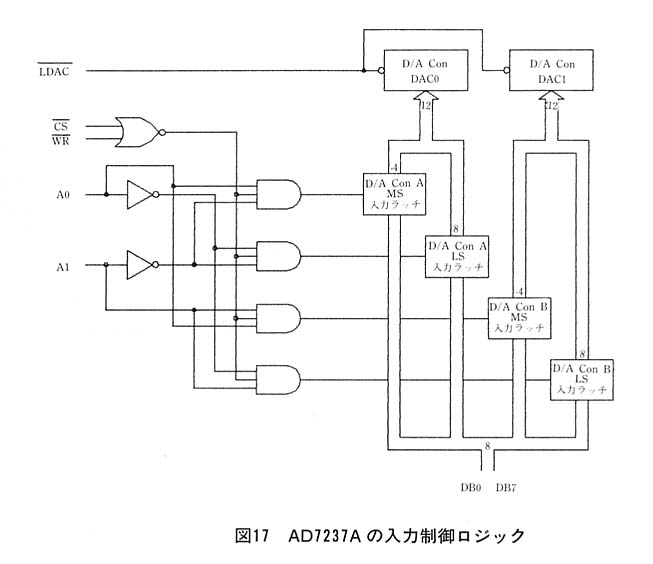

図17にAD7237Aの入力制御ロジックを示す。AD7237Aの入力ロード構成方式は,8ビット幅のデータバスとインターフェースできるよう設計されている。前述のように,このデバイスの分解能は12ビットであるため,ディジタルデータをコンピュータからロードするためには2回に分けて転送する必要がある。そのため,12ビットデータの下位8ビットおよび上位4ビットをラッチする2個の入力ラッチが用意されている。これら入力ラッチ内にある分割されたデータは,DACラッチに送られ,そのデータだけがデバイスからの出力を決定する。

入力ラッチのデータ送信は,CS,WR,A0,A1信号により制御される。CSはチップセレクト信号であり,この入力がアクティブのとき,このデバイスが選択される。WRは書き込み入力であり,この入力がアクティブのときのみ,データを各入力ラッチに転送できる。また,A0,A1はアドレス入力であり,デバイス内の入力ラッチのアドレスが以下のように割り当てられている。

A1=0,A0=0…LS入力ラッチ(CH 0)

A1=0,A0=1…MS入力ラッチ(CH 0)

A1=1,A0=0…LS入力ラッチ(CH 1)

A1=1,A0=1…MS入力ラッチ(CH 1)

これらのアドレスにデータを転送することにより,入力ラッチにそれぞれ4ビット,8ビットデータが格納される。なお,この時点では処理データをラッチしただけであり,これらのデータによってアナログ出力が変化することはない。

LDACは入力ラッチからDACラッチヘの12ビットのデータの転送を制御する。この入力がアクティブになれば,CS,WRがHIGH状態のとき,入力ラッチからDACラッチヘ12ビットのデータが転送され,同時にアナログ出力が更新される。

(2) D/A変換回路について

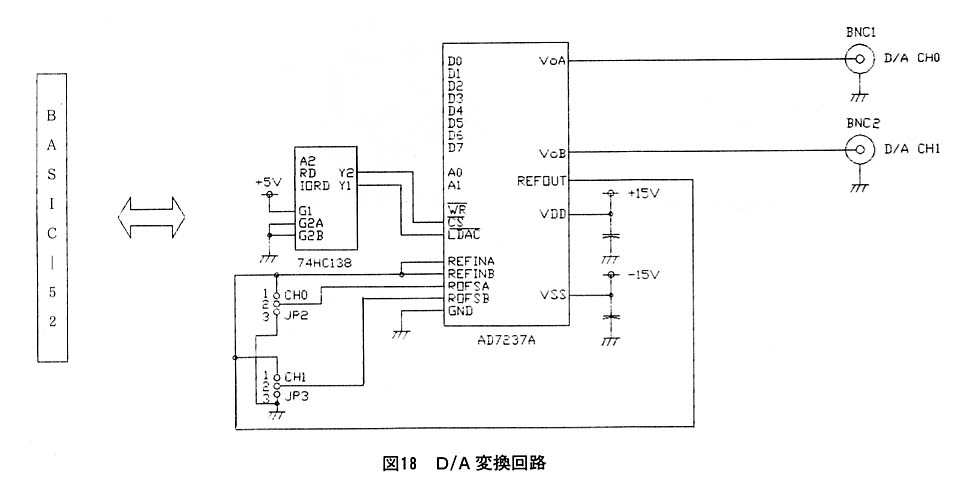

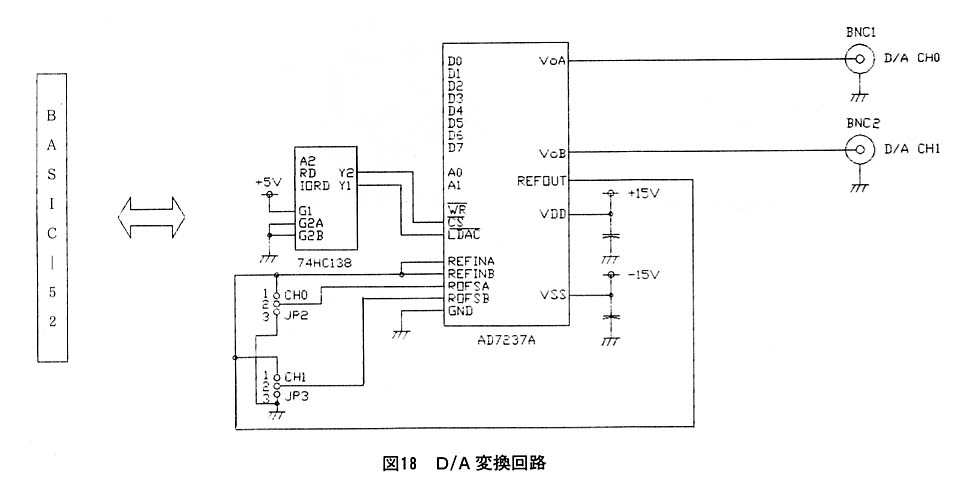

図18にマイコン実験装置に組み込まれているD/A変換回路を示す。この回路はマイコン側から入力されるディジタル信号を,AD7237Aによりアナログ信号に変換してBNC端子に出力する。アナログ出力電圧レンジの選択は,出力アンプの非反転入力端子の接続先を切り替えることにより行う。図18のなかのジャンパSW(JP2およびJP3)の2番ピンと3番ピンをジャンパ接続すると0~+10Vのユニポーラ設定になり,1番ピンと2番ピンを接続すると-5V~+5Vのバイポーラ設定となる。本装置ではバイポーラ出力を実現しているため,出力アンプには±15Vのデュアル電源を使用している。なお,この回路では3種類のアナログ出力範囲のうち0~+5Vのユニポーラ設定は提供されていない。

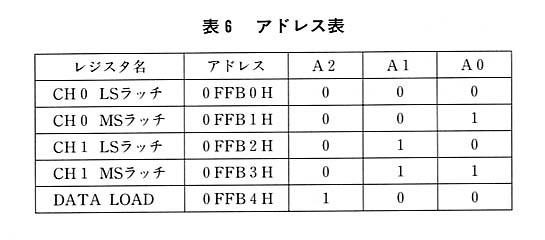

本回路には,前節のパラレルインターフェース回路と同様に,各レジスタにアドレスが設定されている。2個のD/Aコンバータの上位4ビット入力ラッチ,下位8ビット入力ラッチにはA0,A1により設定されたアドレスが割り当てられている。またデータロードレジスタはLDAC信号により選択される。LDAC信号はマイコン側より送られてくるアドレス信号A2などをデコーダによりデマルチプレクスすることにより得られる。これらの信号の関係は電圧レベルでは相反しており,A2信号がHIGHのときLDAC信号はLOWとなる。これは,アドレス信号A2がHIGHのときデータロードレジスタが選択されることを意味する。表6に基準アドレスを0FFB0Hとしたときの各入力ラッチとデータロードレジスタのアドレスを示す。

(3) プログラム例

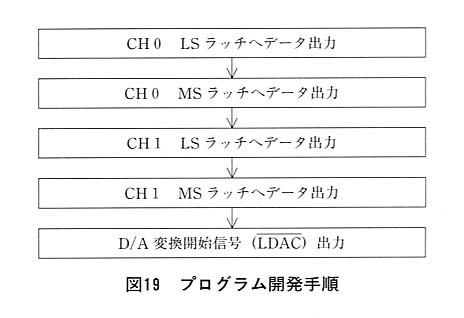

D/A変換素子であるAD7237Aは,前述のように12ビットを8ビットと4ビットに分けてロードするダブルバッファのインターフェース構造を持っているため,ディジタル信号を2分割して送信する必要がある。ディジタル信号を一時記憶する入力ラッチの容量は,8ビットと4ビットであることから,12ビットのディジタル信号は下位8ビットおよび上位4ビットに分割される。そして,これらの信号を入力ラッチヘ送信して,LDAC信号を出力することにより,12ビットのディジタル信号がD/A変換され,同時にアナログ信号が出力される。図19にプログラム開発手順を示す。なお,各入力ラッチヘのデータ転送の順番は任意に決定でき,D/A変換開始信号は2チャンネルに共通して使用することができる。

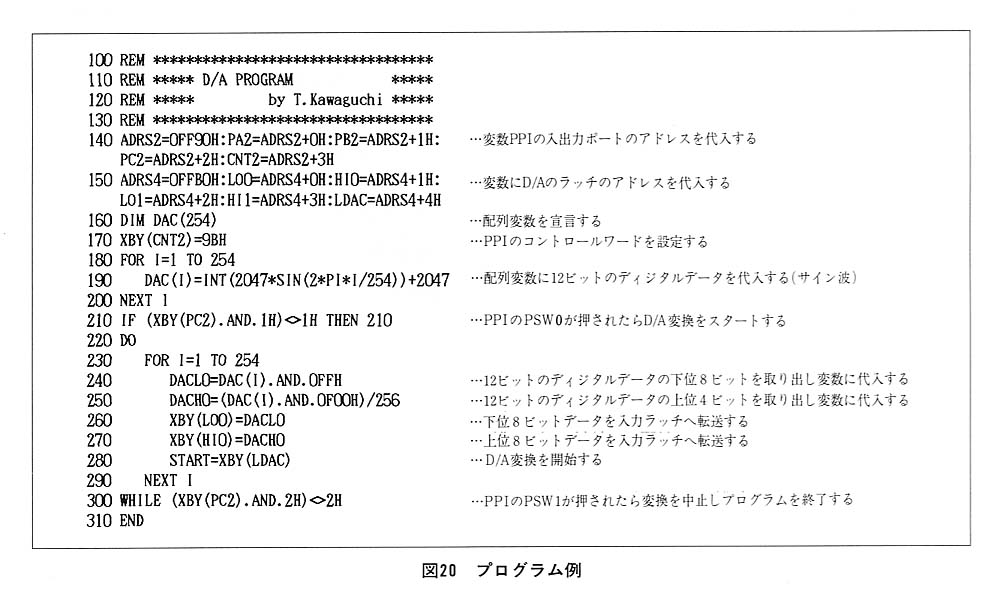

図20にD/A変換回路の制御プログラム例を示す。これは,パラレルインターフェース回路2のポートCに接続されている最下位の押しボタンスイッチPSW0が押されるとサイン波が出力され,PSW1が押されると処理を中止して終了するプログラムである。プログラム中で,12ビットのディジタル信号は0FFH(0000 1111 1111B)で論理積をとることにより下位8ビットに,またF00H(1111 0000 0000B)で論理積をとり256で除して8ビット分右ヘシフトすることにより上位4ビットに分割されている。これらの信号を各入力ラッチヘ送信し,D/A変換開始信号を出力することにより,ディジタル信号がDACラッチヘ転送され,アナログ信号が出力される。

なお,このプログラムではD/A変換回路のアナログ出力範囲は0~+10Vのユニポーラ出力に設定されており,サイン波はハーフスケール分だけオフセットして出力することにより負の領域を確保している。(つづく)